5에서 Amplifier 의 gain 을 늘리기 위한 방법으로 multi-stage 를 이용하는 방법과 cascode 방법에 대해 알아보았습니다. 두 방법 다 많이 사용하는 방법이지만, 공정이 미세화되고 supply voltage가 점점 낮아지면서 cascode 방식은 사용하기 어려워지게 됩니다. mosfet을 stack하면 각각의 단이 차지해야하는 saturation voltage가 있는데 이게 아무리 작아도 0.3V 이상은 필요하기 때문이죠.... 4개의 mosfet만 cascode하더라도 1.2V 이상의 supply voltage가 필요합니다. 따라서 자연스럽게 multi-stage 방식을 이용하여 amplifier의 gain을 증가시킵니다. 하지만 전에도 말했듯이 stage 수를 늘려서 gain을 증가시키는 방식은 closed-loop system에서 unstable할 수 있다는 단점이 있습니다.

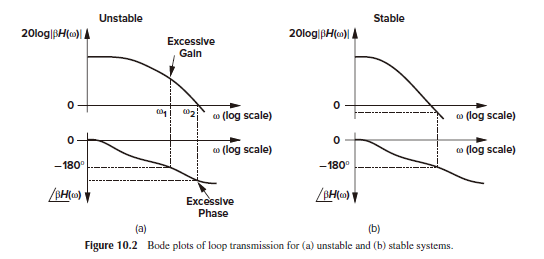

Bode plot으로 frequency response를 보면 Gain이 0일 때의 phase 를 보면 phase margin 을 계산할 수 있습니다. Phase margin은 보통 60도 이상이어야 stable한 시스템이라고 합니다. Unstable 한 시스템은 발진할 수 있기 때문에 위험합니다. 물론 positive feedback 을 걸어 일부러 발진시키는 Ring oscilator 회로도 있지만 일반적인 amplifier에서는 stable한 상황을 원합니다.

Phase margin이 모자라면 step input에 대해 빨리 settle 하지 못하고 ringing이 발생하게 되죠. 따라서 높은 phase margin 확보는 필수적입니다. 여기서 중요한 것이 bode plot은 open-loop에서의 amplifier를 기준으로 그려서 보고 있는겁니다.

Phase margin을 확보하기 위한 방법으로는 위에 보이는 (a)와 같이 gain 자체를 낮춰버릴 수도 있겠죠? 실제 설계시에 저렇게 pole 위치를 유지하면서 gain을 낮추는 거는 어렵기도 하고 gain을 낮춰버리는 것은 우리가 원하는 설계 방향이 아니겠죠. 따라서 (b)와 같은 방법을 사용합니다. 바로 dominant pole을 좀 더 low frequency 쪽으로 낮추는 거죠.

2-stage amplifier 를 예로 들어보겠습니다. 각각의 amplifier 의 output에 pole이 생기므로 2개의 pole을 가진 system이겠죠. dominant pole은 첫 번째 amplifier의 output 단 쪽에서 1/R1C1입니다. Bode plot을 유심히 보면 알겠지만 phase margin에 더 크게 기여하는 것은 dominant pole의 위치입니다. dominant pole이 low frequency에 있으면 있을수록 gain 이 0이 되는 frequency가 더 작아지기 때문이죠. 따라서 우리는 dominant pole을 low frequency 로 보내야합니다. 그렇다면 저항을 늘리거나 cap을 늘려야하는데 보통은 cap을 늘리는게 더 쉽고 간단하죠.

따라서 우리는 두번째 amplifier 의 input과 output 사이에 capacitance를 놓습니다. 이를 miller capacitance라고 합니다. Dominant pole을 low frequency 로 보내기 위해서는 첫번째 stage 의 amplifier output 단의 capacitance 값을 키워야죠. 이 때 키워줘야하는 capacitance 는 수백 fF에서 수 pF까지 키워야합니다. 이정도의 cap은 크기가 정말 어마무시하게 크죠. 따라서 이렇게 큰 capacitor를 달면 면적에서 너무 손해를 보게 되므로 miller cap을 사용합니다.

Miller cap을 이용하면 원래 cap 크기의 (1+Av) 배 만큼 큰 cap처럼 사용할 수 있기 때문이죠. 이를 이용해 dominant pole을 low frequency로 보내버리고 phase margin을 키워 stable 한 system을 만들 수 있습니다.

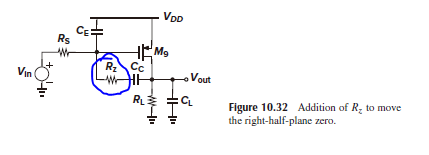

번외로 아래와 같이 miller cap 과 직렬로 저항을 연결하게 되면 zero를 추가할 수 있습니다 zero 의 위치를 움직일 수 있습니다. 이 zero를 이용해 dominant pole과 zero의 위치를 거의 같은 frequency 에 위치시켜 amplifier의 특성을 좋게 하는거죠. 하지만 이는 doublet이 생겨 settling time 이 길어질 수 있다는 단점이 있습니다.

이상입니다.

'반도체 > 전자공학 기초' 카테고리의 다른 글

| Diode란? (1) depletion region, drift & diffusion current, forward & reward bias (0) | 2023.04.23 |

|---|---|

| 5-3. Amplifier 의 Linearity 란?(Nonlinearity 의 원인) Fast Fourier Transform이란? Linearity를 증가시키는 방법 (2) | 2023.04.08 |

| 6. Current mirror (0) | 2023.01.08 |

| 5-1. Amplifier의 gain을 늘려야하는 이유 (0) | 2023.01.07 |

| 5. Gain 늘리는 방법 : Cascode stage vs Multi-stage (0) | 2023.01.03 |