반도체 설계 파트 중 아날로그 설계, 아날로그 설계의 꽃 중 하나인 ADC 에 대해 다뤄보려 합니다. 워낙 깊이 있는 분야이기도 하고 저보다 더 깊은 지식을 갖는 분도 많겠지만, 설계 초보자가 중수 단계로 올라가는데 도움이 되지 않을까 하고 한 글자, 두 글자 꾸준히 써보도록 하겠습니다.

글을 쓰는데 참고한 전공 책은 그 전에 언급한 책들에 Razavi 가 쓴 'Principless of Data Conversion System Design' 입니다.

ADC type : Flash, Pipeline, SAR

해당 글을 읽는 분들은 ADC 의 기본 동작에 대한 기본적인 지식을 갖고 계신다고 가정하고 3가지 가장 정석의 ADC 종류에 대해 다뤄보겠습니다. 바로 Flash, Pipeline, SAR 세가지 입니다.

먼저 ADC performance 중 가장 중요한 Power, Speed, Resolution 관점에서 본 3 종류의 ADC type 은 다음과 같습니다. Power 관점에서는 SAR > Pipeline > Flash 순이고, Speed 관점에서는 Flash > Pipeline > SAR 이며, Resolution 관점에서는 SAR > Pipeline > Flash 입니다. 이는 전체적인 경향성이 이렇다하는 것이지, pipeline ADC 라고 무조건 SAR ADC 보다 resolution 이 낫다 이런 의미는 아닙니다. 밑에서 좀 더 자세히 보죠.

1. Flash ADC

Flash ADC 는 3가지 ADC 중 일반적으로 가장 빠른 ADC 입니다. 일반적인 Flash ADC 구조는 위와 같이 Resistor ladder, Comparator, Encoder 로 이루어져 있습니다. Flash 는 말그대로 각 Binary output 에 해당하는 전압 값을 Resistor ladder 를 이용해 마련한 후, 이를 2^n -1 개의 comparator 를 사용해 7개의 binary bit 을 얻어냅니다. 여기서 N 은 우리가 원하는 resolution 이죠. 3-bit resolution 의 Flash ADC 를 얻고 싶으면 총 2^3 - 1 개, 즉 7개의 comparator 가 필요합니다.

그 뜻은 mid-resolution 인 8bit resolution 을 위해서는 총 63 개의 comparator 가 필요하다는 뜻이며, 이는 엄청난 power consumption 을 의미하겠죠. 결국 Flash ADC 는 다른 ADC 에 비해 power consumption 이 큰 편이며, resolution 이 낮습니다. 하지만 단점이 있으면 장점이 있는 법이죠. Flash ADC 는 첫 번째 단의 S&H 의 speed 에 의해서만 limit 이 정해지기 때문에 속도가 다른 ADC 에 비해 훨씬 더 빠릅니다. 일반적으로 Flash ADC 는 3bit 정도의 낮은 resolution 에 수 GHz 의 speed 의 conversion 이 가능합니다.

2. Pipeline ADC

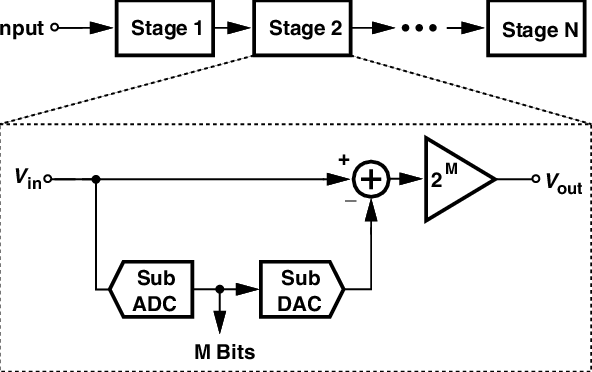

Pipeline ADC 는 위와 같이 여러 개의 stage 를 이용해 conversion 을 하는 ADC 입니다. 한 stage 의 ADC 는 sub - ADC와 sub-DAC 그리고 아날로그 analog subtractor 와 Amplifier 로 이루어져 있습니다. 한 단에서 1bit conversion 을 하게 된다면 첫번째 stage 에서는 MSB 1bit을 판단하게 되고 MSB 가 1 이라면 1bit MSB 에 해당하는 아날로그 전압을 input 전압에서 빼고, 0이라면 input 전압 그대로 amplifier 에 가해 2배 증폭시킨 후 다음단으로 넘기게 됩니다.

Pipeline ADC 의 가장 큰 특징은 여러 개의 stage 에서 나눠서 conversion 을 한다는 점입니다. 따라서 latency 가 긴 대신에, 한 개 stage 의 속도와 같은 속도로 output 을 만들어내죠. 또한 앞 단에서 conversion 을 잘못하게 되면 뒷 단에서 아무리 conversion 을 잘해도 error 가 생기기 때문에 첫 번째 stage 를 가장 잘 설계해야 합니다. 이를 해결하기 위한 방법으로는 redundancy bit 을 이용하는 방법이 있죠. 이는 나중에 또 다뤄보겠습니다.

Pipeline ADC 는 처음 나왔을 때 1개 stage 에서 1개의 bit 만 conversion 하고 대부분 Flash ADC 를 사용하였습니다. 하지만 여러 가지 연구가 진행되고 발전하면서 Pipeline-SAR ADC 등 많은 발전된 형태가 나왔죠. ㅎ하지만 일반적으로 Pipeline ADC 는 Flash 에 비해 power consumption 을 덜 소모하며 SAR 보다는 resolution 이 낮습니다. 일반적인 Pipeline ADC 는 8bit resoultion 등의 설계에 적합하죠. 대신 speed 성능에서 좋은편이여서 수백 MHz 설계에 능합니다.

3. SAR ADC

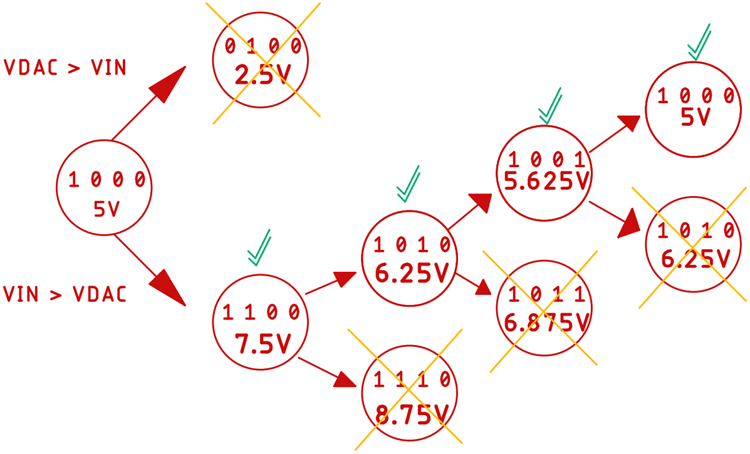

SAR ADC 는 보통 DAC, SAR logic, Sample and hold 와 1개의 comparator 로 이루어져 있습니다. SAR ADC 는 Successive - approximation ADC 의 줄임말로 Flash ADC 와 비슷한 듯 다른 ADC 입니다. 1개의 stage 에서 1bit 씩 한꺼번에 여러 개의 stage 에서 n bit conversion 하는 Pipeline ADC 와 달리 SAR ADC 의 경우 1개의 stage 가 여러 번에 걸쳐서 이진 탐색 기법으로 digital conversion 을 하게 됩니다.

바로 위와 같은 원리가 이진 탐색인데요. MSB 부터 시작해서 한개씩 낮은 bit 를 각각의 bit 에 해당하는 Vdac 값과 Vin 값을 비교해서 input 전압을 digital data 로 conversion 하게 됩니다. 먼저 첫번째로 Vin, input 전압을 sample 합니다. 이는 이진 탐색을 하는 동안 input voltage 가 바뀌면 안 되기 때문이죠. sample 된 전압 값을 처음으로 MSB 가 1인 Vdac 과 비교합니다. 여기서는 1000 에 해당하는 5V 이죠. Vin > Vdac 인 경우에는 Vin 이 5V 이상인 것을 알게 됩니다. 다음 SAR logic 은 input data 를 5V 보다 큰 1100 을 Vdac 으로 보내며 해당하는 Vdac 전압인 7.5V 와 다시 전압을 비교하게 됩니다. 이번에는 Vin<Vdac 으로 나왔습니다. 그러면 비교한 bit 에서 1을 빼 0으로 만들고 그 다음 MSB 를 1로 만들어 비교하게 됩니다.

이렇게 마지막 bit 까지 비교하게 되면 최종 digital code 를 얻을 수 있게 됩니다. 과정에서 보면 알다싶이, SAR ADC 의 경우 다른 ADC 에 비해 input voltage 를 여러번에 나눠서 비교를 하기 때문에 speed 가 가장 느린 편입니다. 대신 1개의 comparator 를 사용해서 n bit conversion 을 할 수 있으므로 power consumption 면에서 가장 훌륭하죠. 일반적으로 SAR ADC 는 수 MHz 이하의 speed 로 사용하며, 잘 설계하면 10bit resolution 의 high-resolution 으로 설계할 수 있습니다.

요즘의 ADC 는 한 가지 방식으로 설계하는 것이 아닌, 여러 개의 방식을 섞어서 설계하기 때문에 설계가 더 어렵습니다. 이럴수록 그 기본이 되는 ADC 종류에 대한 완벽한 이해가 필수겠죠. 앞으로 ADC 의 필수적인 개념에 대해 차차 다뤄보도록 하겠습니다.

'반도체 > 전자공학 심화' 카테고리의 다른 글

| Circuit design : Clock 의 skew 와 jitter (0) | 2024.04.10 |

|---|---|

| Digital 설계 : Latch 와 flip-flop 의 setup & hold margin (0) | 2024.02.13 |

| Comparator 종류 : Continuous-time comparator vs Dynamic comparator (0) | 2023.10.17 |

| Spice & ADE simulation : hspice 에서 alter 구문 사용해서 corner, pvt simulation 돌리는 법 (1) | 2023.10.17 |

| Comparator offset calibration : cap 을 이용한 offset compensation 방법 (1) | 2023.10.11 |