오늘은 Clock signal 의 skew 와 jitter 에 관해 다뤄보겠습니다. 회로를 design 할 때 skew 와 jitter 는 꼭 유의해서 관리해야하는 요소들입니다. 회로의 동작 주파수가 매우 느리다면 skew 와 jitter 에 큰 관심을 가지지 않아도 문제가 없을지 모르지만 주파수가 빨라질수록 회로의 동작에 큰 영향을 끼치죠. 처음에는 좀 헷갈리는 개념이지만 한 번 정리하고 넘어가면 헷갈리지 않을 겁니다. 그럼 먼저 skew 에 대해 다뤄보죠.

1. Skew in Clock signal

skew 의 경우 회로 단에서 설계하는 반도체 설계자에게 꼭 알아야 하는 개념 중 하나입니다. 물론 verilog 를 통한 디지털 설계 시에도 skew 개념을 알면 큰 도움이 돼죠. Skew 는 일반적으로 두 클락 시그널 사이에 생기는 자그마한 time offset, 즉 시간차를 의미합니다. 아래 그래프와 layout을 보시죠.

Vck 라는 clock signal 이 chip 왼쪽에서 생성된다고 가정해봅시다. 우리는 이 클락 시그널을 오른쪽 저 아래 부분에서 필요합니다. 한 눈에 봐도 꽤나 먼 거리를 fly 해야하므로 중간에 signal 이 죽지 않게 inverter 로 buffering 해주어서 보내야하죠. 그렇게 여러 단의 inverter 를 지나쳐 buffering 되어 Vout 이 생겨났다고 해봅시다.

그 때의 Vck 와 Vout 의 waveform 이 위와 같다고 해봅시다. 위 waveform 을 보면 Vck 와 Vout 이 각각 같은 frequency 와 같은 swing range 를 같고 있는 것을 볼 수 있죠. 하지만 Vout 은 Vck 에 비해 delta t 만큼 time offset 이 껴 있습니다. 이를 바로 time skew 라고 하죠. 많은 gate 를 지나면서 RC delay 가 생겼기 때문에 time skew 가 생겼습니다.

그 때문에 우리는 Vout 지점에서 정확히 Vck 를 원하는데 그보다 delay 된 클락을 얻게 되었습니다. 이 time skew 가 clock frequency 보다 현저히 낮을 경우에는 아무 문제가 없을 것입니다. 하지만 time skew 가 훨씬 더 커진다면 큰 문제가 생기겠죠. 잘 이해가 안 갈 수 있으니 예를 한 번 들어봅시다.

먼저 첫번째로 skew 가 clock frequency 보다 훨씬 더 작다고 해봅시다. 예를 들어 clock frequency 의 20%보다도 더 작다고 해보죠.(실제로 주파수와 time 을 비교할 순 없지만 무슨 말인지 이해할거라 생각합니다.) 이 때 Data input 이 두 지점에서 들어오고 각각 latch 된 output 을 두 지점에서 비교해본다고 해봅시다. skew 가 clock 주기보다 훨씬 더 작기 때문에 두 output 은 거의 동시에 latch 된다고 볼 수 있습니다. 그렇게 되면 두 output 을 이용한 연산 시 큰 문제가 없음을 알 수 있습니다.

반면에 이번에는 clock frequency 가 훨씬 더 빨라서 똑같은 skew가 clock 주기의 반정도 된다고 가정해봅시다. 그러면 우리는 Vout 지점에서 같은 clock 을 사용하고 있다고 생각해도 실제로는 약 반주기정도 느린 clk 을 사용하게 돼죠. 결국 이 두 clock 을 이용해 data 를 latch 하고 이를 통해 연산을 할 경우, 그만큼 data window 가 작아질 뿐만 아니라 정확한 연산을 하는 데 훨씬 더 어려움을 겪습니다.

따라서 칩의 크기가 커질수록 그리고 clock 주파수가 빨라질수록 skew 관점에서 생각을 많이 해봐야합니다. 특히 clock 은 계속해서 toggle 하기 때문에 latch 된 output 이 같은 clk 에서 latch 된 것인지 아니면 skew 때문에 밀려서 몇 clk 전이나 후의 clk 으로 채지는지에 대해 꼭 분석해봐야 합니다. 원하는 동작을 제대로 못하고 있을 가능성이 있기 때문이죠.

1. Jitter in Clock signal

다음으로 clock signal 의 jitter 에 대해 알아보겠습니다. jitter 는 일반적으로 PVT variation, 주변 signal 로부터의 interference 등의 여러 요인에 의한 random variation 을 의미합니다. Gate 와 metal loading 에 따른 RC delay 로 명확히 분석할 수 있는 skew 에 비해 jitter 는 그 절대적인 양을 명확히 분석하기는 어렵죠. 이러한 jitter 가 어떤 영향을 끼치는 지 우선 봅시다.

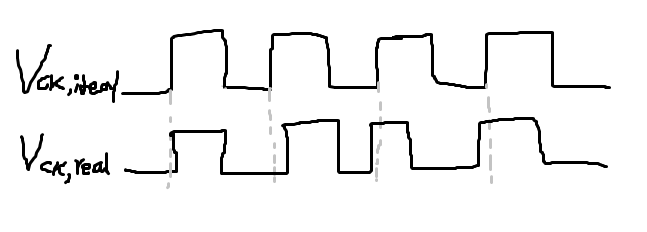

우리가 일반적으로 아는 clock signal은 위와 같습니다. 1GHz 의 ideal 한 clock signal 은 첫번째 rising edge 가 뜨고 정확히 1ns 뒤에 2번째 rising edge, 1ns 뒤에 3번째 rising edge, ... 이런 식으로 ideal 하게 toggle 하죠. 하지만 실제 clock signal 은 다릅니다. 전압 보강을 제대로 못해주었을 경우 toggle 할 때마다 수 mV 정도 supply voltage 가 움직일 수도 있고, 근처 다른 signal 에 의해서 간섭이 있을 수도 있습니다. 그러면 위와 같이 rising edge 가 뜨고 0.99ns 뒤에 2번째 edge 그리고 1.001 ns 뒤에 3번째 edge 이런식으로 edge 가 뜨게 될 것입니다. 이러한 random variation 에 의한 변화를 jitter 라고 합니다. skew 는 전체 clock signal 을 수 ps delay 시키는데 반해, jitter 는 각각의 edge 를 수 ps 정도 random 하게 변화시키죠. 이 때문에 jitter 가 분석하기 더 어렵다는 겁니다.

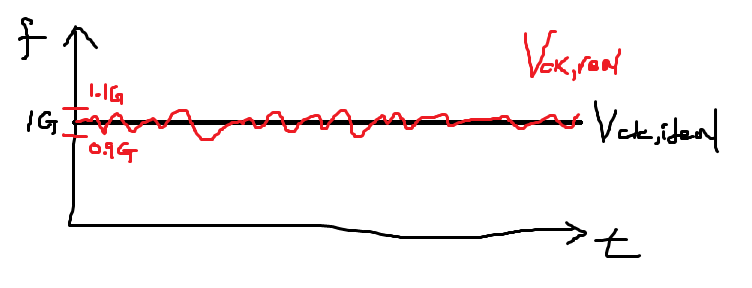

따라서 이러한 jitter 가 낀 real clock signal 을 time 에 따른 frequency graph 를 그려보면 위와 같이 나옵니다. 시간에 따라 주파수가 0.9 ~ 1.1 GHz 까지 변할 수 있죠. 이러한 jitter 는 random 으로 끼기 때문에 random jitter 까지 감안한 simulation 을 해 robust 한 회로를 설계해야 합니다. 이러한 jitter 를 줄이는 방법으로는 PLL, DLL 등을 사용해 깨끗한 clock 을 만드는 방법 등이 있습니다. 이는 다음에 다뤄보도록 하죠.

'반도체 > 전자공학 심화' 카테고리의 다른 글

| Voltage Controlled Oscillator(VCO) 의 개념 및 동작원리 (0) | 2024.06.19 |

|---|---|

| LDO dominant pole 의 위치와 pole compensation (0) | 2024.04.21 |

| Digital 설계 : Latch 와 flip-flop 의 setup & hold margin (0) | 2024.02.13 |

| ADC (1) ADC type - Flash, Pipeline, SAR 개념 설명 및 비교 (2) | 2024.01.28 |

| Comparator 종류 : Continuous-time comparator vs Dynamic comparator (0) | 2023.10.17 |