LDO 를 설계할 때 고려할 점이 몇 가지가 있는데 그 중 하나가 dominant pole 의 위치입니다. 기본적으로 LDO 는 amplifier 가 포함된 feedback system 이기 때문에 stability issue 가 있기 때문이죠.

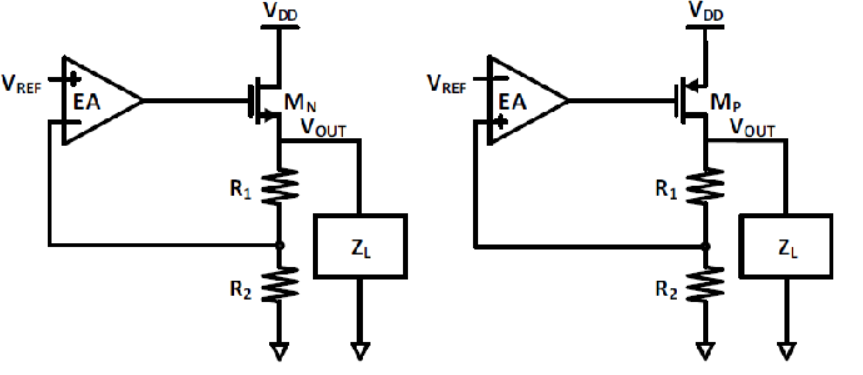

이전 글에도 작성하였지만 일반적으로 LDO 는 pass transistor 로 NMOS 를 쓰는 type 과 PMOS 를 쓰는 타입으로 나뉩니다. pole 은 1/RC 이므로 dominant pole 이 되기 위해서는 해당 node 에서의 cap 이나 저항값이 커야하죠. 때문에 error amplifier 와 pass transistor 의 gate 가 만나는 지점은 대부분 dominant pole 입니다. PMOS 와 NMOS pass transistor 의 차이는 PMOS 의 경우 output 에도 dominant pole 이 위치하여 2-pole system, 그리고 NMOS 는 일반적으로 1-pole system 입니다.

PMOS pass transistor 를 사용한 LDO 의 경우 2-pole system

NMOS pass transistor 를 사용한 LDO 의 경우 1-pole system

전자회로를 배우다 보면 1-pole system 의 경우 stable 합니다. 하지만 2-pole system 부터는 발진할 가능성이 있죠. 따라서 PMOS 를 pass transistor 로 사용할 경우 회로가 발진하지 않도록 load cap 이나 phase compensation 등에 신경을 써주어야 합니다.

PMOS pass transistor 를 사용한 LDO 에서 phase compensation 하기 위해 각 node 의 pole 과 zero 식을 세워보면 위와 같습니다. 정해진 공식에 저항값과 cap 값 등을 대입하면 pole 과 zero 를 구할 수 있습니다.

Stable 한 LDO 를 만들기 위해서는 위와 같이 zero (fz1) 를 2개의 pole 사이에(fp2 와 fp3) 위치시켜야 합니다. 그렇게 하면 2번 째 pole 을 zero 가 어느 정도 phase compensation 시켜주게 되고 이를 통해 stability 를 이뤄낼 수 있습니다.

이런식으로 zero 를 일부러 삽입하는 형태로 phase compensation 을 해주기도 합니다.

'반도체 > 전자공학 심화' 카테고리의 다른 글

| 회로에서의 Look up table (LUT) 의 의미와 사용하는 이유 (0) | 2024.08.30 |

|---|---|

| Voltage Controlled Oscillator(VCO) 의 개념 및 동작원리 (0) | 2024.06.19 |

| Circuit design : Clock 의 skew 와 jitter (0) | 2024.04.10 |

| Digital 설계 : Latch 와 flip-flop 의 setup & hold margin (0) | 2024.02.13 |

| ADC (1) ADC type - Flash, Pipeline, SAR 개념 설명 및 비교 (2) | 2024.01.28 |