SPICE 를 기반으로 하든 ADE 를 기반으로 하든 simulation을 위해서는 netlist가 필요하다. Virtuoso tool 로만 설계를 하고 schematic을 그리고 test bench를 짜서 simulation을 돌리다 보면 netlist에 대한 개념이 모호할 수 있다. 하지만 Virtuoso의 ADE L, ADE XL 등의 tool 도 결국 schematic을 구성한 뒤 저장했을 때 나오는 netlist가 있어야 시뮬레이션을 돌릴 수 있다.

일반적인 Virtuoso simulation을 위한 ideal voltage source 들이다. VDD와 VSS에 각각 supply voltage 와 ground voltage를 공급해주고, 우리가 원하는 signal을 vpwl, vpulse 등의 instance를 사용해 test bench를 짠다. 한 눈에 보기에 직관적이며 따로 가이드라인이 없더라도 10분만에 자신이 원하는 test bench를 짤 수 있을 만큼 편리하다.

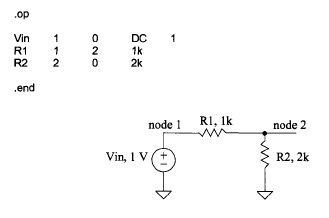

하지만 spice simulation 을 위해 netlist 를 짜는 방식은 상대적으로 직관적이지 않고 또 난이도가 높아 보인다. Spice simulation을 돌리기 위해서는 netlist 파일 뿐만 아니라 test bench 역할을 하는 sp 파일이 필요하다. 위에 보이는 글이 바로 sp 파일이다. Vin 은 우리가 사용하고자 하는 ideal voltage source에 이름을 붙인 것이다. Vsource, Vtemp 등 원하는 대로 이름을 붙여도 된다. 그 뒤 1은 노드 1을 정의한 것이고 0은 그라운드를 정의한 것이다. 결국 첫 번째 줄이 뜻하는 것은 '그라운드(0)와 노드 1 사이에 Vin이라는 소자를 두겠다, 그리고 그 소자는 DC 1V이다' 라는 뜻이다 반대로 R1과 R2는 각각 노드 1과 노드 2 , 노드 2와 그라운드를 연결하는 저항 소자이고 맨 뒤에 나온 1k, 2k는 각각 저항의 크기를 나타낸다.

sp 파일에서 이러한 전압 소자를 어떤 문법으로 사용해야 하는 지에 대해 더 알아보자.

1. pwl 신호

pwl 신호는 특정 시간마다 우리가 원하는 전압을 입력해주는 소자이다.

일반적으로

vin in 0 pwl t0 v0 t1 v1 t2 v2

이런 식으로 나타낸다. 이게 의미하는 바는 '그라운드와 in 노드에 vin이라는 소자를 놓겠다. 그 vin소자는 t0 에는 v0, t1에는 v1, t2에는 v2의 전압을 갖는 pwl 신호다.'라는 뜻이다. 괄호를 사용해도 동작한다.

ex) vin in 0 pwl 0 0 9.9n 0 10n 1

이렇게 하면 0초부터 9.9ns 까지 0V의 전압을 갖다가 10ns에 1V를 갖는 pwl 신호를 뜻한다. 이렇게 되면 0.1ns 에 1V가 증가하는 기울기를 갖게 된다. 100ps에 1V가 증가하는 것은 상당히 reasonable한 값이다. Rising time 과 Falling time 은 공정마다 다르겠지만 미세공정으로는 십수ps 정도밖에 걸리지 않는다. 하지만 이 rising time을 1ps, 100fs 등으로 설정하게 된다면 realistic한 상황을 가정한 시뮬레이션으로 보기에는 어렵다. 이럴 때는 간단한 인버터로 버퍼링 시킨 후에 시뮬레이션을 돌려도 좋다.

2. pulse 신호

pulse 신호는 특정 주기와 특정 pulsewidth를 가진 square wave 신호를 뜻한다. 일반적으로 clock signal을 만들 때 많이 사용하게 되는 신호이다. Rising time과 falling time을 주기의 반으로 갖고간다면 triangle 모양의 wave를 만들 수도 있다.

일반적으로

vclk clk 0 pulse v1 v2 delay tr tf pw period

이런 식으로 나타낸다. 이게 의미하는 바는 '그라운드와 clk 노드에 vclk라는 소자를 놓겠다. 그 vclk 소자는 v1 전압과 v2 전압을 period라는 주기를 갖고 pw라는 pulsewidth를 가지며 tr의 rising time과 tf의 falling time을 갖는 소자이다.'라는 뜻이다.

ex) vclk clk 0 pulse 0 1 0.1n 20p 20p 5n 10n

이런식으로 설정하여 클락 신호를 만들 수 있다.

3. Sine 신호

Sine 신호는 frequency domain에서 설정한 주파수에서만 signal 성분을 갖는 신호이다. 일반적으로

Vin in 0 sin 0 1 200

이런 식으로 나타낸다. DC 성분으로 0으로 갖고 1V의 amplitude를 가지며 frequency 가 200Hz임을 의미한다.

사실 sp 파일은 직접 짜보지 않으면 다소 손에 익지 않고 어려워서 여러 예시 파일을 보고 직접 짜보는게 중요하다. 여러 개의 sp 파일을 짜고나면 문법에 익숙해지기도 하고 새로운 sp 파일을 짤 때 기존에 짰던 파일을 참고해 짜면 소모 시간을 훨씬 줄일 수 있다.

'반도체 > 전자공학 심화' 카테고리의 다른 글

| Antenna effect의 의미 : p-n junction, diode, decoupling cap (0) | 2023.04.16 |

|---|---|

| Tripple well, Deep nwell - Substrate 분리. Deep nwell에 psub 박는 이유 (0) | 2022.12.17 |

| Diode ESD(Electrostatic Discharge) protection - Bonding pad, Bonding wire (0) | 2022.12.17 |

| 회로 Single-ended vs Differential (0) | 2022.09.16 |

| Design consideration & Challenge (0) | 2022.09.12 |