오늘은 디지털회로에서 발생할 수 있는 meta-stability 에 대한 정의에 대해 알아보겠습니다.

디지털 회로를 설계할 시에는 flip-flop 혹은 latch 에서 meta-stable 이 발생하지 않도록 주의하라는 말이 많습니다.

일반적으로 digital 회로를 구성하는 inverter 에는 위와 같은 2 가지 상태가 존재합니다. 바로 VDD 전압인 1 과 VSS 전압인 0 이죠. inverter 는 기본적으로 digital buffer 이기 때문에 output 으로는 0과 1 의 output 만 출력으로 갖습니다. 하지만 data input 이 0과 1이 아닌, 애매모호한 값일 경우, output 또한 0과 1이 아닌 그 중간의 애매한 값으로 출력되게 되죠. 이를 meta-stability 라고 합니다.

meta-stability 상태에서는 위와 같이 0 과 1이 아닌 그 중간의 모호한 값으로 출력되게 됩니다. 이 meta-stability 는 0과 1의 중간값을 갖고 있는 불안정한 상태이며, 위 그림에서 보이는 것과 같이 시간이 지나면 0 혹은 1로 수렴하게 되죠. 하지만 수렴하게 되는 데 까지 시간이 걸리게 되고 이는 digital 회로에서 심각한 error 를 유발할 수 있습니다.

이러한 meta-stable 의 원인으로는 보편적으로 setup / hold time violation 이 있습니다. setup / hold time violation 은 아래 링크 글로 대체하겠습니다.

https://kor-razavai.tistory.com/81

디지털 회로) Setup time과 Hold time의 정의와 violation

오늘은 디지털 회로의 setup time, hold time 의 정의와 violation 에 대해 다뤄보겠습니다. Setup time, hold time 은 디지털 회로에서 알맞은 data 가 넘어가기 위해 꼭 지켜야 하는 요소입니다. 이러한 setup / ho

kor-razavai.tistory.com

Setup / hold time violation 이 일어나 meta stability 가 일어난 걸 timing diagram 과 같이 설명해보죠.

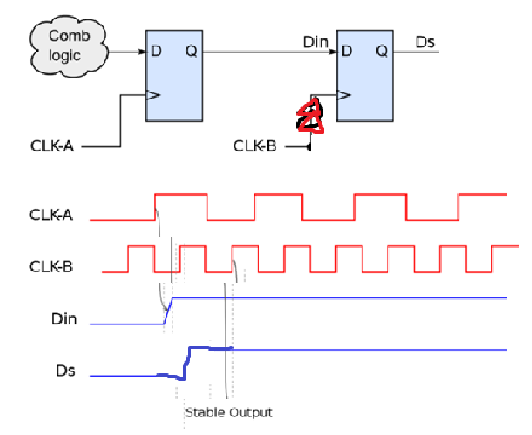

다음과 같이 CLK-A 로 채는 flip-flop 뒤에 CLK-B 로 채는 flip-flop 이 온다고 가정해봅시다.

CLK-A 의 rising edge 로 정렬된 Din data 가 두 번째 flip-flop 에 들어가게 되죠. 이 때 CLK-B 의 rising edge 가 CLK-A 의 rising edge 와 timing 차이가 거의 안 나게 되면 두 번째 flip-flop 에서 setup time violation 이 일어나게 됩니다. tsetup 이 너무 적게 확보된 거죠. 이렇게 되면 두번째 flip-flop 의 output 인 Ds 에서 meta stable 한 output 이 나오게 됩니다. 결국엔 1로 수렴하게 되지만, clk rising edge 가 발생하고 한참 지난 후에야 1 로 수렴하게 됩니다.

그렇다면, 이 meta-stability 를 해결하기 위해서는 어떻게 해야할까요?

여기서는 2가지 해결법을 제시해보죠. 먼저 첫 번째로 setup / hold time 을 좀 더 확보해 meta-stability 를 없애는 방법입니다.

아까 두번째 flip-flop 에서 meta stability 가 발생하는 원인으로는 뒷단 flip-flop 에서 setup time 이 충분히 확보되지 않았기 때문입니다. 따라서 우리는 setup time 을 더 확보함으로써 meta stability 를 없앨 수 있습니다. 가장 쉬운 방법은 CLK-B 에 delay 를 좀 더 추가하여 clk 을 미는 방법이죠. CLK 이 더 밀리게 되면 data 는 그대로임으로 setup time 이 더 확보됩니다. 따라서 Ds 에 meta stability 가 제거되고 stable 한 output 이 나오게 되죠.

다음으로 제시할 방법은 뒷 logic 에 flip-flop 을 더 추가하여 meta-stability 를 없애는 방법입니다.

위와 같이 Ds 를 다시 CLK-B 로 채는 flip-flop 을 한 단 더 추가하는 겁니다. 이렇게 할 경우 여전히 Ds 에는 meta stable 한 output 이 발생하지만, 이를 다시 챈 Dout 에는 meta stable 한 output 이 제거되고 stable 한 output 이 생성됩니다. 2번째와 3번째 flip-flop 을 같은 clk 으로 챘기 때문에 meta stability 를 제거할 수 있는거죠.

이렇게 clk 혹은 data 에 delay 를 추가함으로써 meta stability 를 제거하거나 뒷단에 flip-flop 을 더 추가하여 meta stability 를 제거할 수 있습니다. digital circuit 에서 발생한 meta stability 는 회로에 error 를 발생시킬 수 있으므로 꼭 제거해야 합니다. 다음에 기회가 된다면 meta-stable 을 없앨 수 있는 다른 방법과 reset / set 에 의해 발생할 수 있는 meta stability 에 대해 더 다뤄보겠습니다.

'반도체 > 전자공학 심화' 카테고리의 다른 글

| Layout mismatch 와 Matching 기법 - common centroid 와 interdigitated layout (0) | 2026.01.23 |

|---|---|

| Tri-state inverter 와 Tri-state buffer 개념과 역할, 차이점 (0) | 2026.01.14 |

| 디지털 회로) Flip-flop 에서의 Setup time과 Hold time 정의와 violation 의미 (0) | 2025.12.28 |

| 아날로그 회로) Decoupling cap 이 필요한 이유와 역할 (0) | 2025.02.14 |

| Circuit technique - Power gating (0) | 2025.01.06 |