오늘은 디지털 회로의 setup time, hold time 의 정의와 violation 에 대해 다뤄보겠습니다.

Setup time, hold time 은 디지털 회로에서 알맞은 data 가 넘어가기 위해 꼭 지켜야 하는 요소입니다. 이러한 setup / hold time 은 일반적으로 flip-flop 이나 latch 에서 많이 따지게 됩니다. 이러한 flip-flop 과 latch 는 synchronized 회로에서 필수적이며 아직 개념이 덜 잡혀있으면 아래 글 참고하시면 됩니다.

https://kor-razavai.tistory.com/60

Latch, Flip-flop 회로와 TSPC(True single phase clock) 회로

이번엔 digital circuit 에서 가장 중요한 회로 요소 들인 latch 와 flip-flop 에 대해 다뤄보겠습니다. 0과 1의 신호만 존재하는 digital 회로에서 synchronize 해서 신호를 보내는 것은 정말 중요합니다. 이 때

kor-razavai.tistory.com

일반적인 flip flop 의 경우 input data 인 "D" 와 data 를 채기 위한 clk 인 "CLK" 그리고 flip-flop 의 output 인 "Q"로 구성됩니다. 여기서 flip-flop 과 latch 는 edge-triggered 냐, level-triggered 냐의 방식에 따른 차이가 존재하죠.

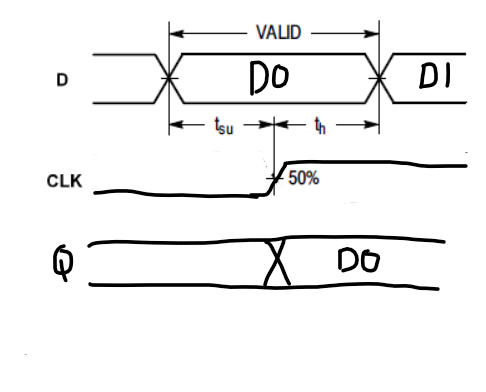

이 때 input data D 와, 이 input 을 채기 위한 CLK 이 다음과 같이 timing diagram 을 갖는다고 생각해봅시다. input data 는 D0, D1 으로 구성되어 있고, 회로는 clk 으로 D0 의 data 값을 채야 합니다. 이 때 clk 의 rising edge 기준으로 D0 data 시작 부분까지를 tsu (setup time) 그리고 clk 의 rising edge 기준으로 D0 data 끝 부분까지를 th (hold time) 이라고 합니다. 여기서는 flip-flop 을 가정했기 때문에 clk 의 rising edge 기준으로 setup / hold time 을 측정하였습니다.

그래프상으로는 setup time = hold time 으로 보이며 flip-flop 이 충분히 잘 data 를 챌 수 있을 것으로 보이죠.

하지만 setup time 이나 hold time 이 부족해 violation 이 일어나면 문제가 생깁니다.

먼저 setup time violation 이 일어나는 case 를 보겠습니다.

위와 같이 clk 이 D0 와 거의 같이 들어온다고 생각해봅시다. 그럼 setup time 은 너무 조금 확보되고 hold time 은 너무 많이 확보되게 됩니다. 이러한 경우를 setup time violation 이라고 하죠. 이 경우에는 output 인 Q 값이 metastable 상태에 들어갈 수도 있고, D0 이전 값인 D-1 값을 챌 수도 있습니다.

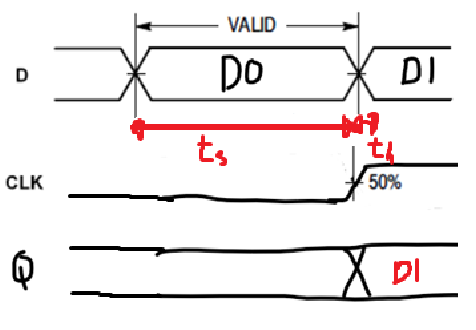

이번엔 hold time violation case 를 보죠.

CLK 이 채야하는 data 인 D0 에 비해 너무 많이 밀리게 되면 hold time violation 이 일어나게 됩니다. 이 경우 setup time 은 너무 많이 확보되고 hold time 은 상대적으로 작게 되죠. 이 경우에는 앞번과 마찬가지로 flip-flop 이 metastable 한 상태로 가거나 그 뒷 data 인 D1 을 채게 됩니다. 따라서 setup / hold time violation 둘 중 어느 하나라도 발생하면 우리가 채려는 D0 값이 아닌 다른 data 를 채게 되서 문제가 발생하게 되죠.

이 때문에 synchronized 회로를 설계할 때, 특히 latch 와 flip-flop 에서는 충분한 setup time 과 hold time 을 갖도록 data 와 clk tree 를 구성해야 합니다. 이 외에 추가적으로 data window 가 어떻게 구성되는지, 그리고 clk tree, data tree 를 어떻게 구성해야 할 지에 대한 정보를 위해서는 아래글 참조 바랍니다.

https://kor-razavai.tistory.com/44

Digital 설계 : Latch 와 flip-flop 의 setup & hold margin

일반적으로 digital 설계를 하다 보면 margin 에 대한 분석을 많이 하게 됩니다. Margin 분석은 Latch 내에서 clock 과 data 간의 margin 을 분석하는 경우도 있고 특정 로직 게이트 내에서 signal 간의 선행 관

kor-razavai.tistory.com

'반도체 > 전자공학 심화' 카테고리의 다른 글

| Tri-state inverter 와 Tri-state buffer 개념과 역할, 차이점 (0) | 2026.01.14 |

|---|---|

| Flip-flop, Latch 의 Meta-stability 란 무엇일까? (0) | 2025.12.29 |

| 아날로그 회로) Decoupling cap 이 필요한 이유와 역할 (0) | 2025.02.14 |

| Circuit technique - Power gating (0) | 2025.01.06 |

| Circuit technique - Clock gating (0) | 2024.12.23 |