회로를 실제로 설계할 때 Antenna 라는 단어에 대해 몇 번 들어보셨을 겁니다. 특히 Tape-out 을 나가기 위해 layout을 그리고 DRC를 보다보면 Antenna effect 에 관한 항목이 많이 나오게 됩니다. 과연 Antenna는 무엇일까요?

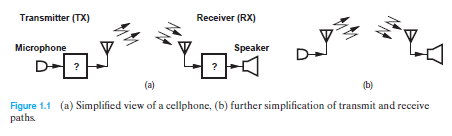

먼저 Antenna하면 가장 많이 떠오르는 것들이 이런 Transmitter나 Receiver일텐데요, Signal을 공기 중으로 쏴서 받는 이런 Antenna는 물론 중요하지만 통신쪽 분들이 설계하고 스펙을 정하는 것일 뿐 저희는 들어온 Signal을 다루기만 합니다. 따라서 별로 관심사가 아니죠. Antenna effect를 다루기 위해서는 먼저 Layout에 대해 짚고 넘어가야 합니다.

먼저 아주 작은 Mosfet 하나가 이렇게 Metal 1에 연결되어 있다고 해봅시다. 매우 큰 영역인 Metal1이 얇은 Metal1을 이용해 mosfet에 연결되어 있죠. 이렇게 되어 있을 때 Metal은 "Antenna"로 동작할 수 있습니다. 큰 메탈 영역에 이온이 쌓이게 되면 포텐셜이 올라가 결국 mosfet의 gate voltage가 감당할 수 있는 것보다 더 커지게 되는거죠. 그렇게 되면 mosfet의 gate oxide에는 breakdown이 일어나게 되고 결국 mosfet을 사용할 수 없게 됩니다. 이는 실제 chip 이 만들어지고 난 후에는 각 metal에 원하는 전압이 가해지니 상관 없는 얘기이지만 fab 과정 중에는 충분히 이뤄질 수 있는 시나리오입니다. Fab 중에는 각각의 metal 이 floating으로 동작하기 때문에 어느 전압 포텐셜을 갖는지 예측할 수 없기 때문이죠!

이러한 Antenna effect는 gate에 어떤 큰 metal 영역이 연결되어 있는 곳은 어디든 발생할 수 있습니다. 이러한 이유 때문에 CMOS technology에서는 이러한 큰 영역의 metal 을 어느정도 제한하게 됩니다. 가장 중요한 gate-oxide가 터지면 chip이 동작할 수 없으니까요. 하지만 실제로 칩을 설계하다보면 큰 Metal 영역이 필요한 곳은 당연히 존재하게 됩니다. 예를 들면 Decoupling cap으로 Mosfet을 사용하게 된다면 Gate와 Source, Drain이 Power에 직접적으로 연결되야하기 때문이죠. 따라서 이러한 경우에는 어떡해야할까요?

이러한 경우에는 Metal 1의 넓은 영역을 일부러 분리시켜줍니다. 이렇게 Metal 2를 이용해서 말이죠. 이렇게 Metal 1을 분리시킨후 Via와 Metal2를 이용해 두 영역을 잇게 된다면 fabrication 중에 Metal1에 높은 potential이 생기더라도 Gate를 파괴시킬 수 없습니다. 왜냐하면 두 Metal1 영역은 물리적으로 떨어져 있기 때문이죠! Metal2와 Via가 박혀야 전기적으로 연결될텐데 Metal 2 fabrication 단계는 Metal1보다 더 나중입니다. 그렇기 때문에 Gate-oxide가 breakdown하는 것을 막을 수 있죠.

하지만 이러한 전략은 항상 사용할 수 있는 전략이 아닙니다. 일반적으로 Metal1 위에는 Metal2가 쓰이고 있을 가능성이 높죠! 위에 Metal2 를 통해 signal 들이 슝슝 날라다니기 때문에 Metal2로 mosfet을 더 넓은 Metal1 영역과 분리시키는 전략은 한정적입니다. 그럼 다른 Metal 층을 이용해 분리하는 방법 말고 어떤 방법이 있을까요?

바로 Diode를 이용하는 방법입니다. 현대 CMOS 공정에서는 diode를 만드는 방법이 간단합니다. Body 가 p-substrate이고 그 위해 P+ 나 N+로 doping하기 때문에 자연스럽게 p-n junction이 생겨나게 됩니다. 따라서 이 p-n junction의 threshold voltage를 넘길 potential 이 쌓이기만 한다면 쌓인 전자가 빠져나가게 되죠. 이를 이용해 다이오드를 문제가 되는 부분에 붙여놓는다면, 넓은 Metal1에 많은 전자가 쌓이게 되더라도 Gate-oxide를 파괴시키기 전에 diode를 통해 body 쪽으로 쭉 흘러나가게 됩니다. Metal1이 아무리 크다고 하더라도 Body에 비하면 바다에 있는 자그마한 섬밖에 되지 않습니다. Metal1에 쌓인 많은 전자가지고는 Body에 큰 영향을 주기 어렵죠. 결국 쌓인 전자를 조그마한 쓰레기통인 Gate-oxide 가 아닌 넓은 쓰레기통인 Body에다가 버려버리는거죠!

따라서 Supply voltage 에서 발생하는 Noise를 없애기 위한 Decoupling cap으로 Mos-cap 을 이용하는 경우 Diode를 꼭 붙여주셔야 합니다. 이러한 Decoupling cap은 supply voltage를 감당하기 위한 매우 넓은 Metal에 연결되어 있기 때문이죠.

이렇게 Layout 상에서 발생하는 Antenna effect를 해결할 수 있습니다. 이상입니다.

'반도체 > 전자공학 심화' 카테고리의 다른 글

| LDO regulator 란? - pass transistor로서의 NMOS와 PMOS 차이 (2) | 2023.04.21 |

|---|---|

| Substrate Latch-up : Latch-up의 의미와 없애기 위한 방법&해결법 (2) | 2023.04.19 |

| Tripple well, Deep nwell - Substrate 분리. Deep nwell에 psub 박는 이유 (0) | 2022.12.17 |

| Diode ESD(Electrostatic Discharge) protection - Bonding pad, Bonding wire (0) | 2022.12.17 |

| 회로 Single-ended vs Differential (0) | 2022.09.16 |