디지털 회로를 설계하다 보면 input driver 와 output driver 를 꼭 신경 써야 합니다. 아날로그 회로를 설계할 때는 대부분 엄청나게 공을 들여 설계를 하다가 간단한 digital 회로의 driver 사이징이 잘못 되어있어 회로가 동작을 안 할수도 있기 때문이죠. 그럼 우선 디지털 회로에서의 driver 에 대해 알아봅시다.

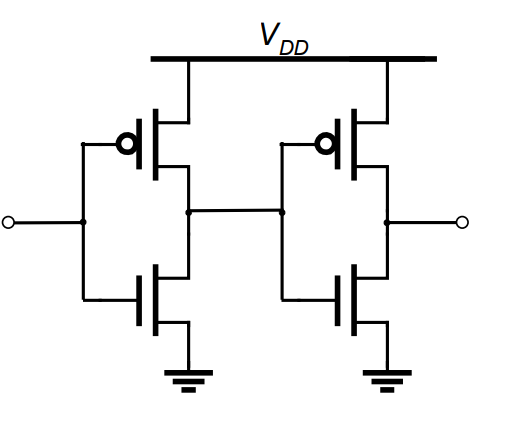

일반적으로 digital 회로에서 driver 라고 하면 인버터를 의미합니다. 다소 간단하죠? 대부분의 디지털 로직은 VDD to VSS 즉 peak to peak signaling 을 하기 때문에, driver 또한 가장 간단하면서도 효율적인 inverter 를 사용합니다. 물론 current 를 아끼기 위해 CML logic 을 사용하기도 하지만, 이는 다음에 다루겠습니다. 그럼 이 간단한 inverter 에서 도대체 어떤 걸 신경써야 할까요? 바로 sizing 입니다.

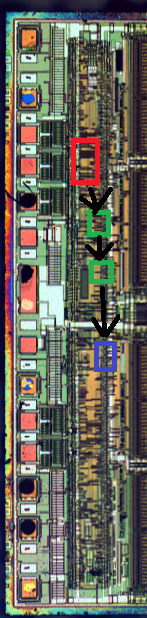

먼저 위와 같은 회로의 layout 을 보겠습니다. Analog 회로 부분은 빼고 digital 회로 부분만 보면 전체적으로logic gate 들로만 이뤄진 것을 알 수 있습니다. 일반적으로 회로를 설계할 때 위와 같이 Adder / MUX 등의 큼직큼직한 블락을 설계하고 이러한 블락들을 회로 상에서 위치시키고 routing 을 진행하게 됩니다. 위와 같이 회로가 작을 때는 상관없지만, 회로가 커지는 경우를 보죠.

그 전의 간단한 회로가 수백개 내지는 수천개 들어간 회로입니다. 한 눈에 봐도 우리가 mosfet 이라고 인식할 만한 transistor 가 수백만개가 있음을 알 수 있죠. 이러한 회로에서는 아날로그 회로는 단순 IO interface 에만 존재할 뿐 대부분 digital signaling 으로 회로를 동작시킵니다. 따라서 수많은 디지털 회로가 안에 존재하게 되죠.

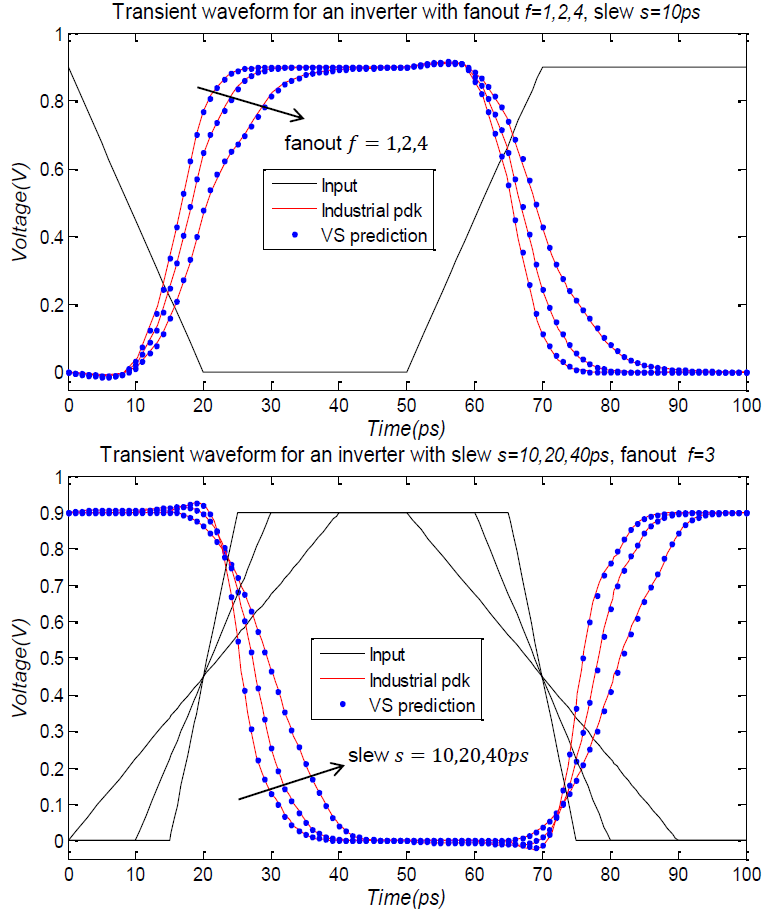

여기서 이제 빨간색 디지털 블락에서 파란색 디지털 블락으로 signal 을 전달해봅시다. Transistor 가 점처럼 보일 정도로 매우 멀리 떨어져 있는 걸 알 수 있는데요. 이럴 경우 transistor 의 gate parasitic cap 보다 signal 이 전달되는데 쓰이는 metal routing 의 parasitic cap 이 엄청나게 크게 됩니다. 따라서 dominant 한 cap 은 metal routing cap 이죠. 그런데 여기서 Output driver 의 size 가 cap 에 비해 작거나 혹은 input driver 의 size 가 크다면 signal slope 이 눕게 됩니다.

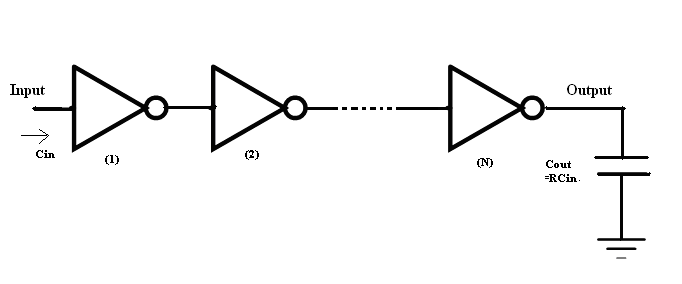

Output driver 가 작을 수록 signal slope 이 눕게 되면서 digital 회로의 pulse 가 점점 더 sine wave 혹은 아날로그 파형처럼 보이게 되죠. 사실 어느 정도 signal slope 이 눕는 것은 불가피합니다. 하지만 speed target 이 몇 GHz 이상인데 중요한 signal 이 몇백 ps 씩 눕게 된다면 아주 치명적이죠. 따라서 이러한 signal 들은 중간에 따로 inverter buffer 를 두어 signal slope 을 개선하기도 합니다.

예를 들면 위와 같이 말이죠. 빨간색 블락에서 파란색 블락으로 digital signal 을 보내야하는데 그 거리가 너무 먼 경우에는 중간중간 초록색 inverter buffer 를 사용하게 됩니다. 당연히 inverter buffer 는 작은 input inverter driver 와 큰 output inverter driver 를 사용하죠.

Fan-out 까지 지켜주어 짝수개의 단으로 inverter buffer 를 꾸며주시면 됩니다. 또한 중요한 signal 의 경우에는 shielding 을 하여 positive coupling 과 negative couplling 으로부터 보호해줘야 합니다. 이상입니다.

'반도체 > 전자공학 기초' 카테고리의 다른 글

| 회로 해석 모델 : Lumped model 과 Distributed model (0) | 2024.09.26 |

|---|---|

| Serializing & Parallelizing : MUX와 DEMUX의 개념과 역할 (0) | 2024.09.24 |

| Logic gate 로직 게이트 쉽게 분석하는 방법 (0) | 2024.09.03 |

| MOSFET 특성 : Input impedance 와 parasitic cap (0) | 2024.06.21 |

| Fast Fourier Transform (FFT) 정리 (0) | 2024.06.17 |