제 블로그에서 이전에도 Current mirror 에 대해 다루긴 했었지만, 오늘은 Current mirror 가 실제로 어떻게 사용되는지에 대해 다뤄보겠습니다. 기존 글을 보고 Current mirror 의 원리와 설계 방법 Cascode 등에 대해 다뤘으나 해당 글만 보고는 왜 Current mirror 를 사용해야 하는 지에 대한 궁금증은 풀리지 않을 수 있습니다.

Current Mirror 원리

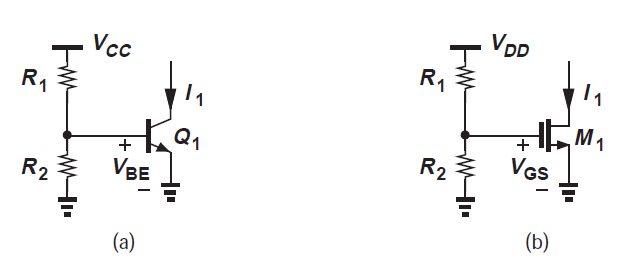

먼저 Current mirror 의 원리에 대해 다시 한 번 다뤄보죠. Current mirror 는 MOSFET 이 특정 고정된 전압의 Vgs 에서 고정된 current 를 흐르게 하는 원리입니다. Ideal 한 mosfet 에서는 Vgs 와 Vth 가 정해진 순간, MOSFET 의 parameter 들은 고정되어 있으므로 변하지 않는 current 가 흐르게 되죠.

이 원리를 이용해 만들어진 것이 바로 위와 같은 Current mirror 입니다. 위와 같이 Iref 가 있을 때, Icopy=Iref 로 만드느 것이 바로 Current mirror 죠.

위와 같이 (b) 가 바로 Reference current 인 Iref 를 흘리는 bias circuit 이고 해당 current 를 복사해오는 Current mirror 는 (c) 와 같이 만들 수 있죠. 이 때 M1 은 Mref 와 비교했을 때 W/L 의 비로 Current 를 복사해오죠.

Current Mirror 를 사용하는 이유

그렇다면 이 Current mirror 를 사용하는 이유가 있을까요? 우린 대부분 Voltage 를 기준으로 biasing 하고 설계하기 때문에 Current mirror 가 필요한 이유가 와닿지 않습니다.

먼저 첫번째 이유로는 Voltage drop 이 있습니다. PCB 상에서든, 칩 안에서의 Power Network 상에서든 저항이 0일 수는 없습니다. 저항이 있으면 전압은 Voltage drop 이 생길 수 있죠. 따라서 우리가 외부에서 1.2V 의 VDD 를 넣어주더라도 실제 원하는 칩 안에서의 블락은 1.2V 보다 더 작은 전압, 즉 1.15 V 를 VDD 로 가질 수도 있죠. 물론 설계 스펙을 널널하게 설계했다면, 1.15V 의 전압 하에서도 동작할 수 있을 것입니다.

실제로 회로가 흘리는 Current 가 크면 클수록 전압 강하는 크게 보입니다. V = IR 이기 때문이죠. 따라서 parasitic resistance 가 매우 작더라도, 사용하는 Current 가 크면 전압 강하는 예상보다 커질 수 있습니다.

하지만 Current Biasing 은 이와 조금 다릅니다. Current biasing 을 하게 될 경우 회로까지 도달하는 데 parasitic resistance 가 있더라도 똑같이 10uA 의 전류가 흐르죠. 이 때문에 Current mirror 를 사용하게 되면 좀 더 정확한 Biasing 을 할 수 있게 됩니다. Voltage biasing 에 비해 좀 더 정확도가 높을 수 있죠. 이 때문에 Low frequency 나 Low power 영역에서는 Current biasing 을 많이 활용합니다. 이상입니다.

'반도체 > 전자공학 심화' 카테고리의 다른 글

| Circuit technique - Power gating (0) | 2025.01.06 |

|---|---|

| Circuit technique - Clock gating (0) | 2024.12.23 |

| LFSR 의 개념과 원리 (Linear Feedback Shift Register) (0) | 2024.09.23 |

| Coupling noise : Positive & Negative coupling 과 Signal shielding (0) | 2024.09.09 |

| Latch, Flip-flop 회로와 TSPC(True single phase clock) 회로 (0) | 2024.09.07 |