회로 설계할 때 power 를 줄이는 것은 매우 중요합니다.

아날로그 회로이든 디지털 회로이든 대부분 clock signal 이 존재하는데요.

오늘은 power 줄이는 방법 중 clock gating 에 대해 알아보겠습니다.

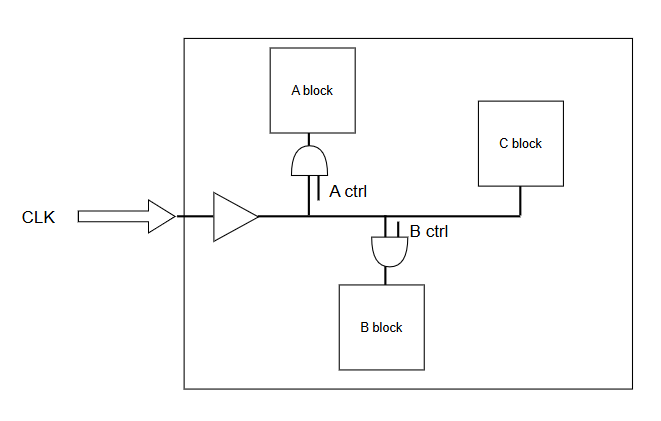

시스템 Clock Tree

회로는 외부에서 CLK 을 공급받아 이를 amplify 시킨 후 chip 내부에서 사용하게 됩니다.

대부분 synchronized system 을 사용하기 때문에 이 clk 을 여러개 block 으로 보내서 사용하는데요.

이러한 모양이 마치 뻗어나온 가지 같다고 하여 Clock tree 라고 표현합니다.

각기 다른 timing 에 동작하는 Block

이러한 clock tree 는 chip 이 크면 클수록 더 멀리 뻗어져 나가고 커지게 되는데요.

High-speed system 에서는 이러한 clock tree 로 인해 power 소모가 엄청나게 커지게 됩니다.

계속해서 빠르게 toggle 하는 clock 은 system 입장에선 낭비이죠.

(만약 clock 이 필요하지 않다면)

위와 같이 CLK 이 계속해서 toggle 하고 있다고 해봅시다.

A block 이 동작해야하는 시간과 B block 이 동작해야하는 시간이 있습니다.

A block 은 앞에 잠깐 동작하면 되고 뒷 부분에서는 동작하지 않아도 되기 때문에 계속 toggle 할 필요가 없죠.

반대로 B는 앞 부분에 toggle 할 필요가 없지만 뒷 부분은 CLK 이 꼭 toggle 해야 합니다.

Clock gating 개념

이제 clock gating 을 해서 power 를 줄여봅시다.

A block 과 B block 의 clock 이 들어가는 곳에 and gating 을 해줍니다.

그 후 각각 A, B block 이 필요한 timing 에 enable 되는 control 신호를 만들어줍니다.

timing diagram 은 아래와 같죠.

A control 신호와 B control 신호 때문에 A clk 과 B clk 은 동작하는 timing 에만 toggle 하게 됩니다.

이렇게 될 경우 전체 clock tree 는 계속해서 toggle 하지만,

A block 과 B block 내부 clk 은 필요한 timing 에만 toggle 하게 되어 power 를 saving 할 수 있죠.

물론 이러한 control, enable 신호를 만드는 추가 logic 이 필요하고 이로 인해 trade-off 가 있습니다.

하지만 High-speed block 에서는 이러한 clock gating 을 통해 엄청난 power saving 을 할 수 있습니다.

이상입니다.

'반도체 > 전자공학 심화' 카테고리의 다른 글

| Decoupling cap 이 필요한 이유와 역할 (0) | 2025.02.14 |

|---|---|

| Circuit technique - Power gating (0) | 2025.01.06 |

| Current biasing : Current mirror 원리와 사용 이유 (0) | 2024.10.02 |

| LFSR 의 개념과 원리 (Linear Feedback Shift Register) (0) | 2024.09.23 |

| Coupling noise : Positive & Negative coupling 과 Signal shielding (0) | 2024.09.09 |