지난번에 이어서, 그리고 마지막으로 MOSFET에 대해 정리해보겠습니다. 기존의 (1), (2) 내용에서 다룬 MOSFET 내용들은 좀 더 기초적인 내용이면서 realistic 한 부분들을 많이 뺀 내용입니다. 기초를 위해서는 꼭 필요한 내용이지만 실제 세상의 회로에서는 조금은 다르게 동작하죠. 이번 내용에서는 realistic 한 회로에서 어떤 일들이 일어나는지에 대해 좀 더 자세히 보겠습니다.

1. Channel Length Modulation (Early effect)

지난번 내용에서 우리는 대부분 Mosfet을 saturation region에서 사용하고 싶어한다는 얘길 했습니다. Saturation region에서는 channel 에 pinch-off 현상이 일어나고 이 때 drain 쪽 channel 이 끊어지게 되면서 depleteion region이 생긴다고 얘기했습니다. 이로 인해 Vds 가 증가하더라도 drain current가 증가하지 않고 Vgs에 의해서만 결정된다고 했었죠. 하지만 실제로도 그럴까요?

실제 Mosfet 모델에서는 조금 다릅니다. 먼저 saturation region에서 동작해 drain 쪽 채널에 pinch-off 현상이 일어났다고 합시다. 위의 그림에서 본 것처럼 채널의 길이가 L보다 조금 더 짧아져 L1이라는 길이를 갖게 되었습니다. 이 때 이 L1 을 effective channel length, Leff 라고도 하죠. 채널의 길이가 짧아지면 어떻게 될까요? Drain current 공식에서 보면 channel length는 식의 분모에 위치해있으므로 전류값이 증가하게 됩니다. 또한 위 그림에서 본 것처럼 Drain의 전압이 커지면 커질수록 depletion region이 더 커지게 되면서 채널 또한 조금 더 짧아지게 됩니다.

따라서 Vds 에 따른 Id curve 를 그려보면 위와 같이 saturation region에서 전류가 일정한 것이 아닌, Vds가 증가함에 따라 전류가 소폭 증가하는 것을 볼 수 있습니다. pinch-off 가 일어나도 effective channel length 가 줄어들어 current가 증가할 수 있는거죠. 이를 Early effect 라고 하며, Channel-length modulation이라고도 합니다.

실제로 반도체 공정이 점점 미세화되고 스케일 다운될수록 gate channel length는 점점 줄어들고 있습니다. 이 줄어드는 length 때문에 channel length modulation의 영향이 더 커지고 있죠. 과거에 채널의 길이가 상대적으로 길었을 때는 drain 쪽에서 depletion region이 커져 channel 의 길이가 짧아지더라도 전체 channel length에 비하면 수%도 안되는 작은 값이었습니다. 따라서 Vds에 따라 전류가 거의 일정하다고 봐도 무방했죠. 하지만 10nm 근처까지 줄어든 공정에서는 이 early effect에 의한 channel length의 변화량이 전체의 십수%나 차지할 정도로 커졌습니다. 이를 더이상 무시할 수 없죠.

따라서 이 early effect를 고려한 새로운 drain current 공식은 다음과 같습니다. Saturation region에서 기존의 공식과 거의 비슷하지만 1+람다Vds 텀이 추가된 걸 볼 수 있습니다. 이 때 저 람다를 얼리 상수라고 합니다. 얼리 상수 도입으로 Saturation region에서도 Vds가 증가함에 따라 전류가 증가하는 것을 볼 수 있습니다.

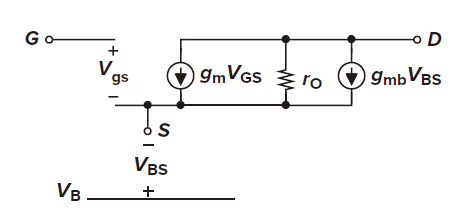

이 Early effect를 고려하게 되면 Mosfet의 small signal model이 다음과 같이 변합니다. 명심하셔야 할 것이 saturation region에서의 분석입니다. 기존에 없었던 Drain node와 Source node 사이에 ro라는 저항이 생기게 됐습니다. 이 ro는 output resistance 라고도 하며 mosfet의 intrinsic output resistance라고 보면 됩니다. 기존의 회로에서 source에서 바라본 저항을 1/gm 이라고 하는데 1/gm 은 수백옴, 내지는 수k옴 정도로 모델링되는 데 반해 이 ro 는 mosfet의 Length가 엄청 짧지 않다면 훨씬 더 큰 값으로 모델링 됩니다. 기본 수백k옴은 되죠. (mosfet의 Length 가 클수록 ro값은 큽니다) Channel length가 무지하게 크다면 이 ro 값 또한 무진장 클것으로 회로 해석에서 무시해도 되죠. 하지만 실제로는 이 ro 값이 무시하기에는 꽤나 작은 값이기 때문에 회로 해석에 꼭 고려하셔야 합니다

(이 ro 저항은 보통 output node 기준으로 Drain에 달리는 저항과 병렬 연결로 해석합니다. 따라서 ro가 크면 클수록 open으로 보여 무시할 수 있지만, ro가 작다면 Drain에 달리는 저항과 병렬 연결돼 크기를 줄일 수 있으므로 영향을 끼치게 됩니다)

2. Transit frequency

Transit frequency는 fT라고도 쓰며, MOSFET에서 small-signal current gain이 unity , 즉 1이 되는 frequency를 뜻합니다. 기초를 다루려고 하다가 본의 아니게 좀 더 어려운 내용으로 넘어왔는데 아래 부분을 스윽 읽어보시고 이해가 안되면 나중에 다시 돌아와서 학습하시길 추천드립니다.

회로를 frequency domain 에서 해석할 때 이 bode-plot을 그려서 해석하게 됩니다. 가장 간단한 Common-source 회로를 생각해보면 Drain node에 1 개의 pole 이 생겨서 위와 같은 bode-plot을 그리게 됩니다. 이를 one-pole system 이라고 하죠. 이 pole을 만나면서 gain은 -20dB의 기울기를 갖고 감소하기 시작하고 결국 20logAv = 0, 즉 Av=1인 지점에 도달합니다. 이때의 frequency를 바로 fT, transit frequency 라고 합니다. (여기서는 이해를 쉽게하기 위해 전압 이득으로 설명했지만 엄밀히 말해서는 small-signal current gain이 1인 frequency입니다)

transit frequency 는 w domain 에서 이렇게 나타납니다. w=2*(pi)*f 이므로 여기서 frequency domain 에서의 transit frequency 또한 알 수 있죠.

이 때 Cgs, Cgd는 MOSFET에서 Gate와 Drain 사이 그리고 Gate와 Source 사이의 parasitic cap을 의미합니다. 이러한 transit frequency를 분석하는 이유는 보다 더 고속으로 회로를 동작시키면서 frequency domain에서 frequency가 높아질수록 mosfet의 특성이 달라지기 때문입니다. 따라서 high-frequency 에서는 mosfet에 대한 보다 정밀한 분석이 필요하죠.

MOSFET의 high-frequency model 은 다음과 같습니다.

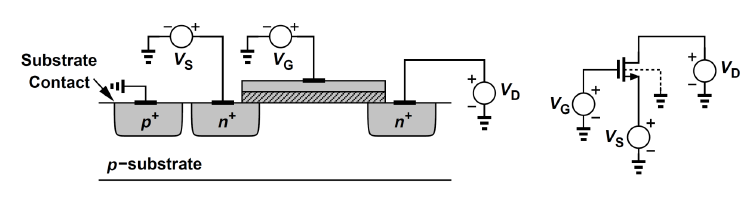

1. Body effect

Body effect는 실제 source의 전압과 p-sub, 즉 body의 전압이 다르기 때문에 발생하는 현상입니다. Mosfet source에 바로 그라운드가 달리고 body 또한 그라운드에 달려있으면 body effect가 없겠지만, 실제로는 mosfet을 cascode하여 많이 사용하기도 하고 fab-out 나갈 때 특정 영역은 body가 그라운드로 단단히 잡혀있지 않을 수도 있기 때문에 body effect를 고려해야합니다.

이는 NMOS에 관한 설명이지만 PMOS에서도 body effect는 존재합니다. Body 와 관련하여 조금 더 깊게 들어가면 body 전압을 분리해주기 위해 tripple well 을 사용하기도 합니다. 처음 설계할 때는 다소 헷갈릴 수 있는 개념이니 다음에 따로 정리해서 올리겠습니다.

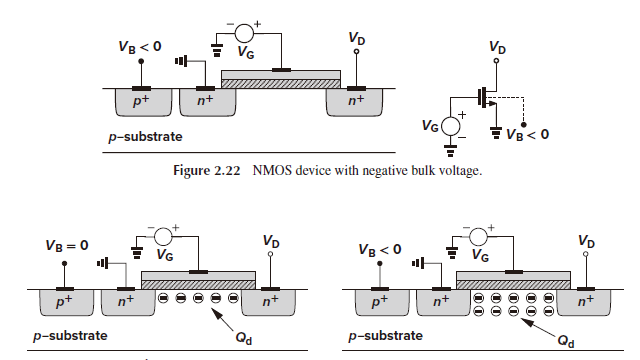

Body effect를 고려하게 되면 위에 보이는 것과 같이 Vth , 즉 threshold voltage term에 body 와 source 사이의 전압차인 Vsb term 이 들어간걸 확인할 수 있습니다.

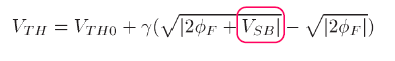

Body effect를 고려했을 때의 MOSFET 그림입니다. Body 전압, 즉 Vb가 음의 값으로 커지면 커질수록 더 많은 hole들이 substrate connection으로 이끌어 당겨집니다. 이로 인해 더 많은 음전하를 남기면서 말이죠. 따라서 depletion region이 점점 더 커지게 됩니다. Depletion region이 커지게 됨으로써 Vth는 증가하게 됩니다.

따라서 정리하면 VB가 줄어들면(음의 방향으로 커지면), Depletion region(Qd)이 증가하게 되고, 이로 인해 Threshold voltage가 커지게 됩니다.

결국 channel-length modulation과 body effect를 모두 고려한 mosfet의 small-signal model은 다음과 같습니다.

이상입니다.

'반도체 > 전자공학 기초' 카테고리의 다른 글

| 3. Small-signal gain (2) gain : small-signal analysis (1) | 2022.10.08 |

|---|---|

| 3. Small-signal analysis : Small-signal gain 구하는 법 (CS,SF,CG) (0) | 2022.09.15 |

| 2. MOSFET이란? (2) Triode, Saturation, Transconductance(gm) (0) | 2022.09.13 |

| 2. MOSFET이란? (1) Length, Width에 따른 변화 (4) | 2022.09.11 |

| 1. Analog design 이란? (0) | 2022.09.10 |